# A zk-evm specification

Olivier Bégassat, Alexandre Belling, Théodore Chapuis-Chkaiban, Franklin Delehelle, Blazej Kolad, Nicolas Liochon

October 2022

# Contents

|  | 6               |

|--|-----------------|

|  | 6               |

|  | 6               |

|  | 7               |

|  | 10              |

|  |                 |

|  | 11              |

|  | 11              |

|  |                 |

|  | 12              |

|  | 14              |

|  | 14              |

|  | 14              |

|  | 15              |

|  | 15              |

|  | 15              |

|  | 16              |

|  | 16              |

|  | 16              |

|  |                 |

|  |                 |

|  |                 |

|  | 19              |

|  | 19              |

|  | 19              |

|  | 20              |

|  | $\frac{1}{21}$  |

|  |                 |

|  | 24              |

|  | 25              |

|  | $\frac{-6}{26}$ |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  |                 |

|  | 01              |

|  |  |  | 20                                                                                                                                                   |

|--|--|--|------------------------------------------------------------------------------------------------------------------------------------------------------|

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  | . 40                                                                                                                                                 |

|  |  |  |                                                                                                                                                      |

|  |  |  | 43                                                                                                                                                   |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  | . 45                                                                                                                                                 |

|  |  |  | . 46                                                                                                                                                 |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  | . 56                                                                                                                                                 |

|  |  |  | . 59                                                                                                                                                 |

|  |  |  | . 63                                                                                                                                                 |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  |                                                                                                                                                      |

|  |  |  | 68                                                                                                                                                   |

|  |  |  | . 68                                                                                                                                                 |

|  |  |  | . 74                                                                                                                                                 |

|  |  |  | . 74                                                                                                                                                 |

|  |  |  | . 74<br>. 76                                                                                                                                         |

|  |  |  | . 74<br>. 76                                                                                                                                         |

|  |  |  | . 74<br>. 76<br><b>80</b><br>. 80                                                                                                                    |

|  |  |  | . 74<br>. 76<br><b>80</b><br>. 80                                                                                                                    |

|  |  |  | . 74<br>. 76<br><b>80</b><br>. 80<br>. 80                                                                                                            |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84                                                                                                         |

|  |  |  | . 74<br>. 76<br><b>80</b><br>. 80<br>. 80<br>. 84<br>. 84                                                                                            |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84                                                                                                 |

|  |  |  | <ul> <li>74</li> <li>76</li> <li>80</li> <li>80</li> <li>80</li> <li>84</li> <li>84</li> <li>84</li> <li>85</li> </ul>                               |

|  |  |  | <ul> <li>74</li> <li>76</li> <li>80</li> <li>80</li> <li>80</li> <li>84</li> <li>84</li> <li>84</li> <li>85</li> </ul>                               |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86                                                                                 |

|  |  |  | <ul> <li>74</li> <li>76</li> <li>80</li> <li>80</li> <li>80</li> <li>84</li> <li>84</li> <li>84</li> <li>85</li> <li>86</li> <li>86</li> </ul>       |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86                                                                         |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86                                                                                 |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87                                                         |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87<br>. 87                                                 |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87<br>. 87                                                 |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87<br>. 88<br>. 88<br>. 88                                 |

|  |  |  | . 744 . 766 . 800 . 800 . 800 . 804 . 844 . 845 . 866 . 867 . 877 . 878 . 888 . 888 . 888 . 888 . 888                                                |

|  |  |  | . 744 . 766 . 800 . 800 . 800 . 804 . 844 . 844 . 856 . 866 . 867 . 877 . 878 . 888 . 888 . 889                                                      |

|  |  |  | . 744 . 766 . 800 . 800 . 800 . 844 . 844 . 856 . 866 . 876 . 877 . 878 . 888 . 889 . 899 . 899                                                      |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87<br>. 87<br>. 88<br>. 88<br>. 88<br>. 89<br>. 89<br>. 90 |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87<br>. 87<br>. 88<br>. 88<br>. 88<br>. 89<br>. 90<br>. 90 |

|  |  |  | . 74<br>. 76<br>. 80<br>. 80<br>. 80<br>. 84<br>. 84<br>. 85<br>. 86<br>. 86<br>. 87<br>. 87<br>. 87<br>. 88<br>. 88<br>. 88<br>. 89<br>. 90<br>. 90 |

|  |                     | 02    |

|--|---------------------|-------|

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     | . 97  |

|  |                     | . 98  |

|  |                     | 99    |

|  |                     | 100   |

|  |                     | 102   |

|  |                     |       |

|  |                     |       |

|  | [2Ful1 ⇒ 3]         |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     | 122   |

|  |                     | 122   |

|  |                     | 123   |

|  |                     | 124   |

|  |                     |       |

|  |                     | 126   |

|  |                     | 126   |

|  |                     | 126   |

|  |                     | 126   |

|  |                     |       |

|  |                     | 129   |

|  |                     |       |

|  |                     |       |

|  |                     | 101   |

|  |                     | 139   |

|  |                     |       |

|  |                     |       |

|  | Column descriptions |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     |       |

|  |                     | . 143 |

|  |  |  |  |  |  |  |  |  |  |  |  | 145 |

|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|  |  |  |  |  |  |  |  |  |  |  |  | 145 |

|  |  |  |  |  |  |  |  |  |  |  |  | 145 |

|  |  |  |  |  |  |  |  |  |  |  |  | 146 |

|  |  |  |  |  |  |  |  |  |  |  |  | 148 |

|  |  |  |  |  |  |  |  |  |  |  |  | 149 |

|  |  |  |  |  |  |  |  |  |  |  |  | 149 |

|  |  |  |  |  |  |  |  |  |  |  |  | 150 |

|  |  |  |  |  |  |  |  |  |  |  |  | 150 |

|  |  |  |  |  |  |  |  |  |  |  |  | 151 |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  | 100 |

|  |  |  |  |  |  |  |  |  |  |  |  | 157 |

|  |  |  |  |  |  |  |  |  |  |  |  | 157 |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  | 163 |

|  |  |  |  |  |  |  |  |  |  |  |  | 163 |

|  |  |  |  |  |  |  |  |  |  |  |  | 163 |

|  |  |  |  |  |  |  |  |  |  |  |  | 163 |

|  |  |  |  |  |  |  |  |  |  |  |  | 165 |

|  |  |  |  |  |  |  |  |  |  |  |  | 165 |

|  |  |  |  |  |  |  |  |  |  |  |  | 165 |

|  |  |  |  |  |  |  |  |  |  |  |  | 166 |

|  |  |  |  |  |  |  |  |  |  |  |  | 168 |

|  |  |  |  |  |  |  |  |  |  |  |  | 168 |

|  |  |  |  |  |  |  |  |  |  |  |  | 170 |

|  |  |  |  |  |  |  |  |  |  |  |  | 171 |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  | 175 |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  |     |

|  |  |  |  |  |  |  |  |  |  |  |  | 176 |

|  |  |  |  |  |  |  |  |  | 176        |

|--|--|--|--|--|--|--|--|--|------------|

|  |  |  |  |  |  |  |  |  | 177        |

|  |  |  |  |  |  |  |  |  | 177        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 178        |

|  |  |  |  |  |  |  |  |  | 178        |

|  |  |  |  |  |  |  |  |  | 178        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 181        |

|  |  |  |  |  |  |  |  |  | 182        |

|  |  |  |  |  |  |  |  |  | 193        |

|  |  |  |  |  |  |  |  |  | 195        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 198        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 224        |

|  |  |  |  |  |  |  |  |  | 224        |

|  |  |  |  |  |  |  |  |  | 235        |

|  |  |  |  |  |  |  |  |  | 235        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 237        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 238        |

|  |  |  |  |  |  |  |  |  | 238        |

|  |  |  |  |  |  |  |  |  | 238        |

|  |  |  |  |  |  |  |  |  | 239        |

|  |  |  |  |  |  |  |  |  | 239        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | <b>240</b> |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 241        |

|  |  |  |  |  |  |  |  |  |            |

|  |  |  |  |  |  |  |  |  | 241        |

|  |  |  |  |  |  |  |  |  | 2/11       |

# Introduction

### 0.1 Purpose

The present document is a revised and expanded version of a previous (partial) specification of a zk-evm.

#### 0.2 Context and results

Rollups are a family of powerful scaling technologies which promise to considerably increase the capacity of the Ethereum Blockchain. An introduction to Rollups, zk-EVMs and their role in improving Ethereum capacity can be respectively found in [1, 2]. Multiple attempts at building scalable and practical rollup solutions have been positively received. zkSync [3], for instance, transpiles Yul into a zk-VM friendly bytecode. Cairo [1], on the other hand, uses a custom architecture adapted to an efficient STARK prover for smart contracts written in Cairo . Other projects, such as Hermez [5] or Scroll Tech [1] and this project aim to interpret native EVM bytecode, without transpilation or further compilation steps.

#### 0.3 Conventions

Throughout the document we use a number of notational conventions which we explain here. These conventions apply to column names and are meant to clarify the origin and purpose of certain columns within a given trace. Others should be viewed as constructors which define new columns from existing ones.

Modules have three letter identifiers. The named modules are the following:

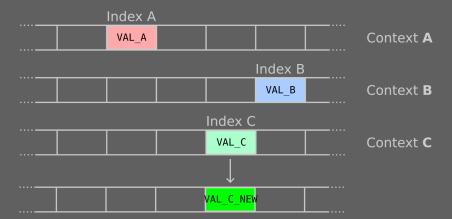

Module stamps. Module stamps count calls to a given module; most modules have a single stamp though the hub and ALU have several. Stamp columns are adorned with a □, thus the STO□ is the module stamp of the storage module. Module stamps are typically computed/updated in the hub module whose main purpose is to dispatch (paid for an otherwise valid) instructions to the module(s) that are equipped to carry them out. Associating a unique identifier (i.e. stamp) to such "module-calls" is crucial when the order of operations matters. This is the case for instructions pertaining to (address) warmth (i.e. the WRM module), required gas computations (i.e. GAS), RAM (i.e. MMU and RAM), the stack (i.e. HUB), storage (i.e. STO), ... to cite a few. Stateless modules such as the modules handling arithmetic (i.e. the ALU module), binary (i.e. BIN) or word comparison (i.e. WCP) opcodes don't require a time stamp per se yet are given one nonetheless. (e.g. the address warmth module corresponds to the three letter identifier WRM); the corresponding stamp column is that identifier followed by □ (e.g. HUB□).

Imported columns. Angular parentheses  $\langle \cdots \rangle$  signal columns whose contents are imported from other modules by means of a lookup argument. By way of example: all modules  $^{1}$  import their module stamp from the hub. Modules tasked with executing certain opcodes will typically import values from the stack (e.g. pairs of stack values  $\langle {}_{k}\mathsf{VAL}^\mathsf{hi} \rangle, \langle {}_{k}\mathsf{VAL}^\mathsf{lo} \rangle$ , for various  $k \in \{1, 2, 3, 4\}$ .) Many modules also imports values that aren't borrowed from the stack. E.g. the hub module imports the instruction  $\langle \mathsf{INST} \rangle$  from the ROM, e.g. the GAS module imports the current, new and endowment gas values  $(\mathsf{GAS}^\kappa, \mathsf{GAS}^\nu)$  and  $\mathsf{GAS}^\kappa$  respectively) from the hub, e.g. the OOB module imports execution context dependent data such exception flags, the size of return data  $\langle \mathsf{RDS} \rangle$ , the size of call data  $\langle \mathsf{CDS} \rangle$  or the code size  $\langle \mathsf{CODESIZE} \rangle$ .

**Decoded columns.** A particular case of the above arises with **decoded columns**. Those are columns whose contents are extracted from a hardcoded collection of columns using a lookup argument. They are adorned with a lozenge as in  $^{\Diamond}$ COL. By way of example: the hub contains various instruction decoded flag columns but also a  $^{\Diamond}$ STACK\_PATTERN column whose contents are deduced from an immutable reference table called the **instruction decoder**. Similarly the binary module imports the results of binary operations performed on pairs of bytes (and injects the relevant one into the result.)

Flag columns. Among the instruction decoded columns on finds various binary flags columns (e.g.  $^{\Diamond}$  ALU  $\bowtie$ ,  $^{\Diamond}$  MMU  $\bowtie$ ,  $^{\Diamond}$  EXP  $\bowtie$ , ...). These serve several purposes. The first is to provide an *indication* as to when modules *may* be sollicited by the hub to carry out an instruction. Thus arithmetic instructions raise the  $^{\Diamond}$  ALU  $\bowtie$ , instructions that involve the RAM raise the  $^{\Diamond}$  MMU  $\bowtie$  etc ... Other flags trigger particular behaviours. For instance the PUSH  $\bowtie$  and the JUMP  $\bowtie$  trigger the expected behaviour of the program counter in the hub.

Module selector columns. When an instruction raises an instruction flag the associated module may get triggered. The actual trigger is usually deduced form this flag and exception flags. Such columns are tagged with a  $\P$  symbol

Interleaved columns. Certain arguments require us to merge columns of the same size into a single column. We use  $\boxplus$  to signify the formation of such interleaved columns. E.g. starting with columns A, B and C of size n we may form the column  $X := A \boxplus B \boxplus C$  defined as having length 3n and values

$$\begin{cases} \mathsf{X}_{3\cdot i+0} = \mathsf{A}_i \\ \mathsf{X}_{3\cdot i+1} = \mathsf{B}_i \\ \mathsf{X}_{3\cdot i+2} = \mathsf{C}_i \end{cases}$$

Row permutations. Our arithmetization requires row permutation arguments. These usually take the following form: we are given a small family of reference columns  $\mathsf{REF}_1, \ldots, \mathsf{REF}_p$  of equal size n (which we view as the columns of a  $n \times p$  reference matrix  $\mathsf{REF}$ ). We are further given the description of an essentially unique permutation of the set  $\{0, 1, \ldots, n-1\}$  of rows indices, e.g. "(the essentially unique) row permutation of the matrix  $\mathsf{REF}$  under which its rows appear lexicographically sorted". We then write  $\mathsf{AUX}_j \mapsto [\mathsf{AUX}_j]^{\mathsf{XZ}}$  for the mapping which takes an arbitrary column of the same size and applies the aforementioned row permutation to its rows.

## 0.4 Organization

- 1. ALU: ALU module; deals with opcodes performing arithmetic operations; see chapter ??;

- 2. BIN: binary module; deals with opcodes performing binary operations; see chapter ??;

$<sup>^{1}</sup>$  which are connected to the hub

- 3. WCP: word comparison module; deals with opcodes performing integer comparisons; see chapter 9:

- 4. MXP: computes memory expansion costs; may raise a flag if offsets are wildly out of bounds; see chapter 6;

- 5. GAS: module which performs gas checks at crucial points in time; performs the (63/64)-ths computations for CALLs and CREATES; computes associated gas endowments; see chapter ??gas;

- 6. ROM: contains the bytecodes which are run and or (temporarily) deployed in a batch of transactions; see chapter 4;

- 7. HUB: module containing the stack and call stack; dispatches instructions to other modules; see chapter 1;

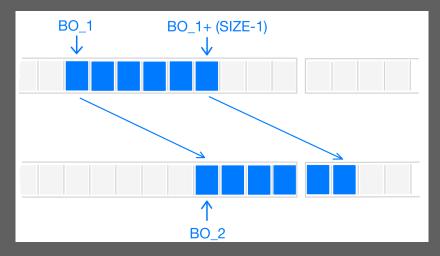

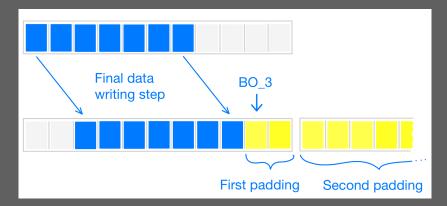

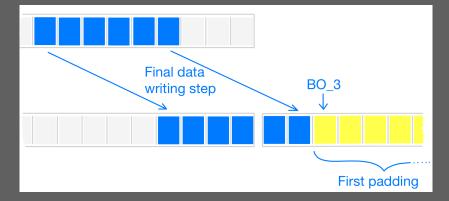

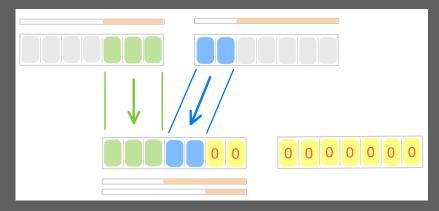

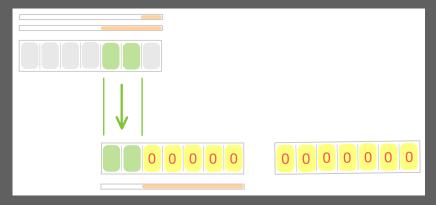

- 8. MMU: first stop in the life time of an opcode execution which touches RAM; performs arithmetic on offsets and various sizes to cut down execution of a single opcode into a sequence of smaller queries; see chapter 2;

- 9. RAM: contains the RAM of all execution context and can communicate with other data sources such as ROM and other data stores; carries out the sequence of small queries commissioned by the MMU; see chapter 3;

- 10. OOB: performs certain range checks required by instructions; see chapter 5;

- 11. STO: storage module; unique among all modules other than the hub in that it computes its own gas costs; see chapter 8;

- 12. ACC: address existence module; loads and udpates account data from the state; WIP;

- 13. WRM: address warmth module: loads prewarmed addresses; handles address warmth in general; built on similar principles as the storage module; see chapter ??;

The following are a few very small modules that either perform a very specific task or are used for reference for the prover

- 1. KEC: two simple modules: an INFO-module which extracts informations for whenever Keccak is executed in the zk-evm (i.e. paid for executions of SHA3 and CREATE2) such as the size in bytes of the data to hash<sup>2</sup>; the second module serves as a data store to which to extract the message to hash;

- 2. LOG: same idea for logs; the information module extracts the log parameter ( $\in \{09, 1, 2, 3, 4\}$ ), logger address and size in bytes; the second module serves as a data store for the log message;

- 3. EXP: computes the dynamic gas cost of the EXP instruction; see chapter ??;

- 4. SHV: shaves the leading 12 bytes off addresses; see chapter 13;

$<sup>^2</sup>$ The price, which depends on the *number of EVM words* rather than the *number of bytes*, is computed in the MXP

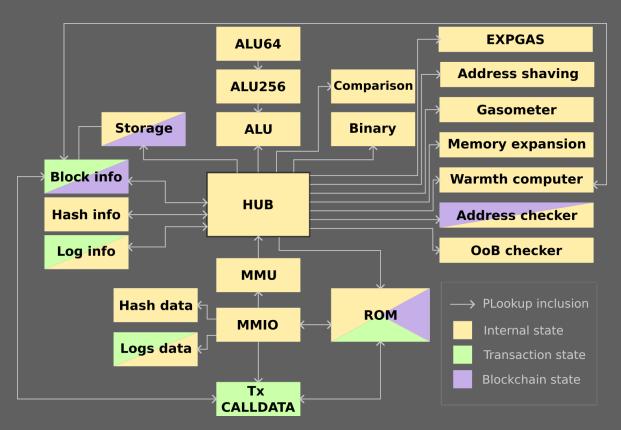

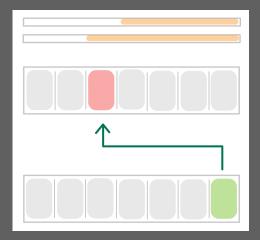

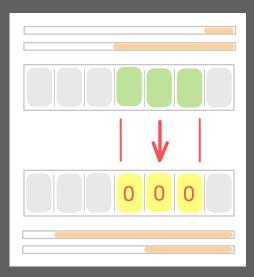

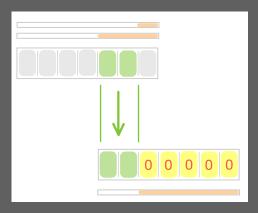

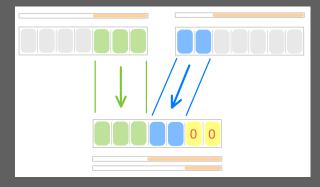

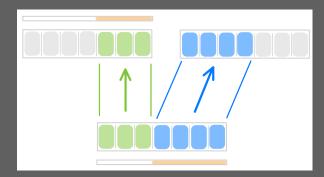

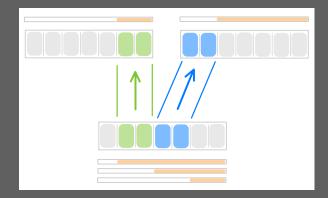

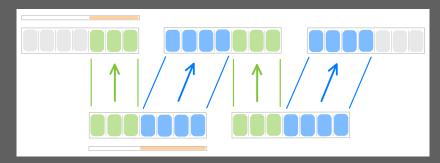

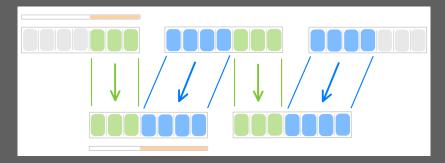

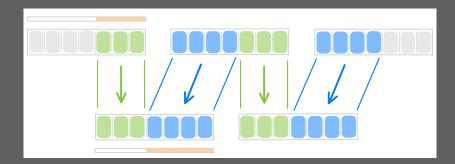

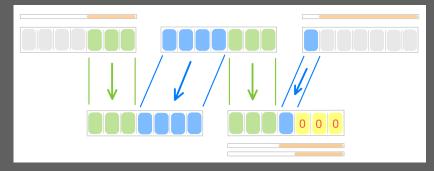

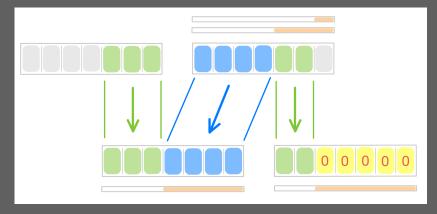

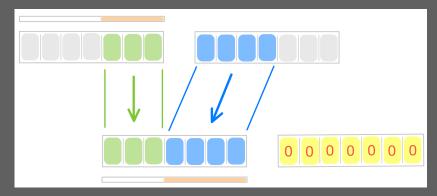

Figure 1: Modular architecture of the zk-evm. Boxes represent modules and arrows represent (plookup) inclusion proofs. If an arrow points from module ABC to module XYZ then XYZ imports a portion of its data from ABC. Arrows may be bidirectional which signals a "bilateral" inclusion proof.

### 0.5 Suggestions for reading this document

We suggest the reader start with the chapter on the **hub** 1. The hub is the center piece of our zk-evm design. It reads instructions from the **ROM** 4 and dispatches instructions to other modules. Various smaller modules which are directly connected to the hub (e.g. the word comparison module or out of bounds module 5) may prove helpful to develop some intuition for the techniques used elsewhere. After the hub, the main module of interest is certainly the RAM. In our design the RAM is split into 2 pieces: the memory management unit 2 (or offset processor) and the memory mapped input output module??. The **mmu** receives instructions from the hub and is tasked with breaking them down into smaller "elementary" operations. This reduction is a two phase process: the first phase ("precomputation" or "establishing" phase) extracts auxiliary data from the arguments of the opcode (offset and size parameters). The second "micro-instruction writing" phase uses these numerical parameters to build a sequence of micro-instructions (**surgeries** and **transplants**) which the **mmio** imports and carries out.

The reader should be warned: this document is a work in progress: typos — even outright mistakes — are to be expected. One module (the **address existence** module) is presently missing from the spec — it is a work in progress. Some sections have received more attention than others. The **hub** 1, the memory-mapped-input-output module?? are among them as are various other "smaller" modules such as the binary module, the word comparison module and others.

## Chapter 1

# Hub

#### 1.1 Columns

#### 1.1.1 Conventions

Throughout the document we use a number of notational conventions which we explain here. These conventions apply to column names and are meant to clarify the origin and purpose of certain columns within a given trace. Others should be viewed as constructors which define new columns from existing ones.

Modules have three letter identifiers. The named modules are the following:

Module stamps. Module stamps count calls to a given module; most modules have a single stamp though the hub and ALU have several. Stamp columns are adorned with a □, thus the STO□ is the module stamp of the storage module. Module stamps are typically computed/updated in the hub module whose main purpose is to dispatch (paid for an otherwise valid) instructions to the module(s) that are equipped to carry them out. Associating a unique identifier (i.e. stamp) to such "module-calls" is crucial when the order of operations matters. This is the case for instructions pertaining to (address) warmth (i.e. the WRM module), required gas computations (i.e. GAS), RAM (i.e. MMU and RAM), the stack (i.e. HUB), storage (i.e. STO), ... to cite a few. Stateless modules such as the modules handling arithmetic (i.e. the ALU module), binary (i.e. BIN) or word comparison (i.e. WCP) opcodes don't require a time stamp per se yet are given one nonetheless. (e.g. the address warmth module corresponds to the three letter identifier WRM); the corresponding stamp column is that identifier followed by □ (e.g. HUB□).

Imported columns. Angular parentheses  $\langle \cdots \rangle$  signal columns whose contents are imported from other modules by means of a lookup argument. By way of example: all modules  $^{\dagger}$  import their module stamp from the hub. Modules tasked with executing certain opcodes will typically import values from the stack (e.g. pairs of stack values  $\langle {}_k \text{VAL}^{\text{hi}} \rangle, \langle {}_k \text{VAL}^{\text{lo}} \rangle$ , for various  $k \in \{1,2,3,4\}$ .) Many modules also imports values that aren't borrowed from the stack. E.g. the hub module imports the instruction  $\langle \text{INST} \rangle$  from the ROM, e.g. the GAS module imports the current, new and endowment gas values  $(\text{GAS}^\kappa, \text{GAS}^\nu)$  and  $(\text{GAS}^\kappa)$  respectively) from the hub, e.g. the OOB module imports execution context dependent data such exception flags, the size of return data  $\langle \text{RDS} \rangle$ , the size of call data  $\langle \text{CDS} \rangle$  or the code size  $\langle \text{CODESIZE} \rangle$ .

**Decoded columns.** A particular case of the above arises with **decoded columns**. Those are columns whose contents are extracted from a hardcoded collection of columns using a lookup argument.

<sup>&</sup>lt;sup>1</sup>which are connected to the hub

They are adorned with a lozenge as in  $^{\diamond}COL$ . By way of example: the hub contains various instruction decoded flag columns but also a  $^{\diamond}STACK\_PATTERN$  column whose contents are deduced from an immutable reference table called the **instruction decoder**. Similarly the binary module imports the results of binary operations performed on pairs of bytes (and injects the relevant one into the result.)

Flag columns. Among the instruction decoded columns on finds various binary flags columns (e.g.  $^{\Diamond}$ ALU  $\bowtie$ ,  $^{\Diamond}$ MMU  $\bowtie$ ,  $^{\Diamond}$ EXP  $\bowtie$ , ...). These serve several purposes. The first is to provide an *indication* as to when modules may be sollicited by the hub to carry out an instruction. Thus arithmetic instructions raise the  $^{\Diamond}$ ALU  $\bowtie$ , instructions that involve the RAM raise the  $^{\Diamond}$ MMU  $\bowtie$  etc ... Other flags trigger particular behaviours. For instance the PUSH  $\bowtie$  and the JUMP  $\bowtie$  trigger the expected behaviour of the program counter in the hub.

Module selector columns. When an instruction raises an instruction flag the associated module may get triggered. The actual trigger is usually deduced form this flag and exception flags. Such columns are tagged with a 7 symbol

**Interleaved columns.** Certain arguments require us to merge columns of the same size into a single column. We use  $\boxplus$  to signify the formation of such interleaved columns. E.g. starting with columns A, B and C of size n we may form the column  $X := A \boxplus B \boxplus C$  defined as having length 3n and values

$$\begin{cases} \mathsf{X}_{3\cdot i+0} = \mathsf{A}_i \\ \mathsf{X}_{3\cdot i+1} = \mathsf{B}_i \\ \mathsf{X}_{3\cdot i+2} = \mathsf{C}_i \end{cases}$$

Row permutations. Our arithmetization requires row permutation arguments. These usually take the following form: we are given a small family of reference columns  $\mathsf{REF}_1, \ldots, \mathsf{REF}_p$  of equal size n (which we view as the columns of a  $n \times p$  reference matrix  $\mathsf{REF}$ ). We are further given the description of an essentially unique permutation of the set  $\{0,1,\ldots,n-1\}$  of rows indices, e.g. "(the essentially unique) row permutation of the matrix  $\mathsf{REF}$  under which its rows appear lexicographically sorted". We then write  $\mathsf{AUX}_j \mapsto [\mathsf{AUX}_j]^{\mathsf{XC}}$  for the mapping which takes an arbitrary column of the same size and applies the aforementioned row permutation to its rows.

#### 1.1.2 Column descriptions

- 1. INSTRUCTION\_STAMP: instruction stamp column; abbreviated to INST $\square$ ; the first instruction takes place at INST $\square = 1$ ; increases by 1 with every instruction;

- 2. STACK\_STAMP: stack stamp column; abbreviated to abbreviated to STACK $\square$ ; the first operation touching the batch's first transaction's root context's stack has  $\square$ STACK=1; increases by one every time the stack is *popped*, *peeked at* or an item is *pushed* onto the stack;

How many **stack items** an instruction touches depends on the instruction itself; consecutive values of  $\Box$ STACK may jump by any value in the range  $\{0, 1, 2, 3, 4, 5, 6, 7, 8\}$ ; the precise amount by which it jumps is decided by the **stack pattern** which the instruction follows.

- 3. HEIGHT: contains the current height of the current execution context's stack; the height is in the range  $\{0, 1, \dots, 1024\}$  with HEIGHT = 0 signifying an empty stack;

- 4.  $\mathsf{HEIGHT}^{\bar{\nu}}$ : contains the height of the current execution context's stack after dealing with the current instruction;

- 5. (INST): instruction loaded from the ROM;

- 6.  $\langle INSTRUCTION\_ARGUMENT \rangle^{hi}$ ,  $\langle INSTRUCTION\_ARGUMENT \rangle^{lo}$ : instruction argument (for PUSH\_X instructions) loaded from the ROM; abbreviated to  $\langle ARG \rangle^{hi}$  and  $\langle ARG \rangle^{lo}$  respectively;

- 7. STATG: instruction decoded static gas cost of instruction;

- 8. OINST\_PARAMETER: instruction parameter obtained from instruction decoding (INST); abbreviated to OPARAM:

- 9. \$\footnote{\text{TWO\_LINE\_INSTRUCTION}}\$: instruction decoded binary flag indicating whether an instruction requires one or two rows in the execution trace; abbreviated to \$\footnote{\text{TLI}}\$;

- 10. COUNTER: binary counter column; abbreviated to CT;

For one line instructions (i.e.  ${}^{\Diamond}\mathsf{TLI}_i = 0$ ) we have  $\mathsf{CT}_i = 0$ ; for two line instructions (i.e.  ${}^{\Diamond}\mathsf{TLI}_i = 1$ ) counter will count from 0 to 1 (i.e.  $\mathsf{CT}_i = 0$  and  $\mathsf{CT}_{i+1} = 0$  if we enter the instruction at row i).

- 11. STACK\_PATTERN: instruction decoded "stack pattern" column; defines the pattern according to which stack values are touched or left empty; abbreviated to PAT

- 12.  $^{\Diamond}\mathsf{FLAG}^1, ^{\Diamond}\mathsf{FLAG}^2, ^{\Diamond}\mathsf{FLAG}^3$ : three isntruction decoded binary flag columns;

For instance the  ${}^{\Diamond}$ PARAM associated with DUPX,  $X \in \{1, 2, ..., 16\}$ , is X - 1 while the  ${}^{\Diamond}$ PARAM associated with SWAPX,  $X \in \{1, 2, ..., 16\}$ , is X. In our model, a stack item is fully determined by 6 parameters: the context number CONTEXT\_NUMBER (i.e. CN) and 5 other parameters which we describe below, though the stack items of a given row all share the same CN. We say that a stack item was touched by an instruction if it was either peeked at, popped or pushed onto stack. Every row of the present module touches up to 4 stack items. An instruction whose (instruction decoded)  $^{\Diamond}$ TWO\_LINE\_INSTRUCTION flag equals 0 can touch, in one way or another, up to 4 stack items; instructions whose (instruction decoded)  ${}^{\diamond}\mathsf{TWO}$  LINE INSTRUCTION flag equals 1 can touch, in one way or another, up to 8 stack items spread over 2 consecutive rows of the execution trace. Among the instructions raising the  $^{\Diamond}$ TWO\_LINE\_INSTRUCTION one finds all variations on CALL, the LOG0-LOG4 instructions but also CREATE and CREATE2. The former is nonnegotiable as these instructions pop 6 or 7 items from stack and push a "success bit" onto it (which amounts to 7 or 8 touched stack items). The LOGO, LOG1, LOG2 instuctions touch (pop) 2, 3 and 4 stack items respectively while LOG3, LOG4 touch (pop) 5 and 6 stack items respectively. The CREATE and CREATE2 instructions touch 4 and 5 stack items respectively. For simpler constraints we have chosen a uniform approach to all logs where the first row of the intruction touches (pops) the offset and size parameters and the next row touches

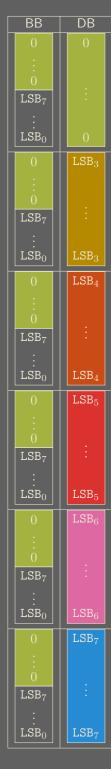

The next 20 (!) columns contain information about the stack items an instruction touches. These 20 columns are comprised of 4 batches (parametrized by k = 1, 2, 3, 4) of 5 columns.

- 13. <sub>k</sub>HEIGHT: column containing the height  $\in \{1, ..., 1024\}^2$  of the k-th touched stack item;

- 14. <sub>k</sub>VAL hi: column containing the

- 15. <sub>k</sub>VAL lo: column containing the

- 16.  $_k\mathsf{POP}$ : binary column;  $_k\mathsf{POP}=1$  indicates that the item at height  $_k\mathsf{HEIGHT}$  was popped;  $_k\mathsf{POP}=0$  indicates that the item at height  $_k\mathsf{HEIGHT}$  was peeked at or pushed;

- 17.  $^{\square}_{k}$ STACK: stack stamp;

The stack stamp columns will be used in the stack consistency constraints to impose a total order on the accesses to a given stack height of a given execution context. The pop flag will oscilate like so: 0 (i.e. push), 1 (i.e. pop),  $0, 1, \ldots$

$<sup>^2</sup>$ Note the range difference between the  $_k$ HEIGHT columns and the HEIGHT column.

- 18. STACK\_EXCEPTION: binary column; lights up precisely when an instruction raises a stack exception; depending on the instruction this is either a stack overflow or a stack underflow (or both in the case of DUP\_X instructions); abbreviated to STX;

- 19. STACK\_UNDERFLOW\_EXCEPTION: binary column; lights up precisely when an executing the current instruction would produce a stack underflow exception; abbreviated to SUX;

- 20. STACK\_OVERFLOW\_EXCEPTION: binary column; lights up precisely when an executing the current instruction would produce a stack overflow exception; abbreviated to SOX;

- 21. HEIGHT\_UNDER: used purely for detecting stack underflows; takes values in the range  $\{0, 1, \dots, 1024\}$ ; abbreviated to HU;

- 22. HEIGHT\_OVER: used purely for detecting stack overflows; takes values in the range  $\{0, 1, \dots, 1024\}$ ; abbreviated to HO;

#### 1.2 Stack

#### 1.2.1 Heartbeat

This section describes the hearbeat of the stack module. It is imposed by two factors: the instruction decoded binary column  ${}^{\Diamond}\mathsf{TWO}_{\mathsf{LINE\_INSTRUCTION}}$  and the INSTRUCTION\_STAMP. The COUNTER column either stagnates at 0 if  ${}^{\Diamond}\mathsf{TLI}_i = 0$  or counts from 0 to 1 if  ${}^{\Diamond}\mathsf{TLI}_i = 1$ . There are one or more padding rows at the beginning.

- 1.  $\mathsf{INST}\square_0 = 0$ ;

- 2. INST $\square$  is nondecreasing in the following sense:  $\forall i$ , INST $\square_{i+1} \in \{\mathsf{INST}\square_i, 1 + \mathsf{INST}\square_i\}$ ;

- 3. IF  $INST\square_i = 0$  THEN  $^{\Diamond}TLI_i = 0$ ;

- 4. IF  $\Diamond \mathsf{TLI}_i = 0$  THEN  $(\mathsf{CT}_{i+1} = 0 \text{ AND } \mathsf{CT}_i = 0)$ ;

- 5. IF INST $\square_i \neq 0$  THEN IF  $^{\diamondsuit}$ TLI $_i = 1$ :

- (a) IF  $CT_i \neq 1$  THEN

$$\begin{cases}

\operatorname{INST}_{i+1} = \operatorname{INST}_{i} \\

\langle \operatorname{INST} \rangle_{i+1} = \langle \operatorname{INST} \rangle_{i} \\

\operatorname{CT}_{i+1} = 1 + \operatorname{CT}_{i}

\end{cases}$$

Note that in that case  ${}^{\Diamond}TLL_{i+1} = {}^{\Diamond}TLL_i$  as well. Actually

$$\Diamond$$

DECODED\_COLUMN<sub>i+1</sub> =  $\Diamond$ DECODED\_COLUMN<sub>i</sub>

for any instruction decoded column.

$$\text{(b)} \ \ \mathbf{ir} \ \mathsf{CT}_i = 1 \ \ \mathbf{THEN} \ \left( \mathsf{CT}_{i+1} = 0 \ \ \text{ and } \ \mathsf{INST}\square_{i+1} = 1 + \mathsf{INST}\square_i \right).$$

#### 1.2.2 Counter constancy

We say that a column X is counter-constant if it satisfies

$$\mathsf{CT}_i \neq 0 \implies \mathsf{X}_i = \mathsf{X}_{i-1}$$

Note  $\langle \mathsf{INST} \rangle$  is counter-constant by construction, see section 7.3.1. It follows that all instruction decoded flags are counter-constant. The following columns are counter-constant:

1. HEIGHT 2. HEIGHT $^{\nu}$  3. HU 4. HO

#### 1.2.3 Height range

We ask that the HEIGHT column satisfy the bound

$$\forall i, \left\{ \begin{aligned} & \text{HEIGHT}_i \\ & \text{HEIGHT}_i^{\nu} \\ & \text{HU}_i \\ & \text{HO}_i \end{aligned} \right\} \in \{0,1,\dots,1024\}.$$

We test this by means of a Cairo-style small-range range-proof. Note that our arithmetization requires no further range check on the  $_k\mathsf{HEIGHT},\ k=1,2,3,4,$  columns. The above constraint is sufficient to enforce that:

- if the k-th stack item is nonempty then  $_k$ HEIGHT  $\in \{1, ..., 1024\}$ ;

- if the k-th stack item is mostly empty or empty then  $_k\mathsf{HEIGHT}=0.$

#### 1.2.4 Zero padding

Beyond the heartbeat constraints and range constraints that take effect with the first row of the execution trace, all constraints detailed below apply under the assumption that

$$\boxed{ \left[ \mathsf{INST} \square_i \neq 0 \right] }$$

In our implementation the execution trace of this module, like that of any other module, is padded with at least one row of zeros so that its length may hit a power of 2. In our implementation we include the following extra constraint for every column X of the module

IF

$$INST\square_i = 0$$

THEN  $X_i = 0$

#### 1.2.5 Stack exceptions

Before the stack excavates any items it must first check whether doing so would cause an exception, i.e. a stack overflow or a stack underflow. The present section takes care of this check. It uses the HEIGHT column and instruction decoded evm parameters  $(\delta_w, \alpha_w)$  which occupy the  $^{\Diamond}$ DELTA and  $^{\Diamond}$ ALPHA columns respectively. and

1. We first check for stack underflows:

$$HU_i = (2 \cdot SUX_i - 1) \cdot (^{\Diamond}DELTA_i - HEIGHT_i) - SUX_i$$

- 2. If  $SUX_i = 1$  Then  $SOX_i = 0$  (i.e. if a stack underflow occurred we set the overflow flag to 0.)

- 3. IF  $SUX_i = 0$  THEN we check for overflows:

$$\mathsf{HO}_i = (2 \cdot \mathsf{SOX}_i - 1) \cdot (\mathsf{HU}_i + ^{\Diamond} \mathsf{ALPHA}_i - 1024) - \mathsf{SOX}_i$$

Note that  $SUX_i = 0$  implies  $HU_i = \underline{HEIGHT}_i - {}^{\Diamond}\underline{DELTA}_i$ .

4.  $STX_i = SUX_i + SOX_i$ .

By construction one cannot have both a stack overflow and an underflow at the same time. The preceding thus computes the binary flag  $SUX_i \vee SOX_i = SUX_i + SOX_i - SUX_i \cdot SOX_i = SUX_i + SOX_i$ .

#### 1.2.6Call stack depth exception

We provide the constraints for the CSDX flag.

- 1. CSDX is binary

$$CSD_i + {}^{\Diamond}CALL \bowtie_i + {}^{\Diamond}CREATE \bowtie_i - 1025 \cdot CSDX_i \in \{0, 1, \dots, 1024\}.$$

#### 1.3 Stack patterns

#### 1.3.1 Purpose

The present section explores stack patterns and sheds some light as to which instructions use what stack patterns. What we call a stack pattern is the pattern according to which the stack items touched by an individual instruction are laid out across the 4 to 8 stack items which are available to the instruction. Full details are given in section 1.4 on "one line stack patterns" and section 1.5 on "two line stack patterns".

The Ethereum Yellow Paper defines for every instruction w a pair of nonnegative integers  $(\delta_w, \alpha_w)$ where  $\delta_w$  is the number of stack items w pops off the stack and  $\alpha_w$  is the number of stack items w pushes onto the stack<sup>4</sup>. Similarly, every instruction has a corresponding zk-evm specific pair of nonnegative integers  $(\delta_w^{zk}, \alpha_w^{zk})$  which, to some extent, determine the instruction's stack pattern. The pairs  $(\delta_w, \alpha_w)$  and  $(\delta_w^{zk}, \alpha_w^{zk})$  don't necessarily coincide (though they mostly do.) For instance, the following inequalities always hold:

$$\delta_w^{\mathbf{z}\mathbf{k}} \in \{0, 1, \dots, 7\}, \quad \alpha_w^{\mathbf{z}\mathbf{k}} \in \{0, 1, 2\} \quad \text{and} \quad \delta_w^{\mathbf{z}\mathbf{k}} + \alpha_w^{\mathbf{z}\mathbf{k}} \in \{0, 1, \dots, 8\}$$

The most notable divergence between these parameter families comes from DUP\_X and SWAP\_X instructions,  $X \in \{1, \dots, 16\}$ . The Ethereum Yellow Paper ascribes them, respectively, the pairs  $(\delta_{DUP\_X}, \alpha_{DUP\_X}) = (\delta_{DUP\_X}, \delta_{DUP\_X})$ (X, X + 1) and  $(\delta_{SWAP_X}, \alpha_{SWAP_X}) = (X + 1, X + 1)$ . The stack pattern our arithmetization uses bears no dependence on X, as implicitly the zk-evm has:

$$(\delta_{\mathtt{DUP}~\mathtt{X}}^{\mathtt{zk}},\alpha_{\mathtt{DUP}~\mathtt{X}}^{\mathtt{zk}}) = (1,2) \quad \text{and} \quad (\delta_{\mathtt{SWAP}~\mathtt{X}}^{\mathtt{zk}},\alpha_{\mathtt{SWAP}~\mathtt{X}}^{\mathtt{zk}}) = (2,2).$$

In other words the zk-evm views DUP\_X instructions (that don't raise a stack underflow or overflow exception) as the popping of one stack item (at height  $\mathsf{HEIGHT}_i - (\mathsf{X} - 1)$ ) and two pushes (at height  $\mathsf{HEIGHT}_i - (\mathsf{X} - 1)$  and  $\mathsf{HEIGHT}_i + 1$  respectively)<sup>5</sup>. Similarly, the zk-evm views  $\mathsf{SWAP}_{\mathsf{X}}$  instructions (that don't raise a stack underflow exception) as the popping of two stack items (at height  $\mathsf{HEIGHT}_i - \mathsf{X}$ and  $HEIGHT_i$ ) and two pushes (at height  $HEIGHT_i - X$  and  $HEIGHT_i$  respectively)<sup>6</sup>. Note that the parameter to substract from the current height<sup>7</sup> is read off the instruction decoded column <sup>⋄</sup>PARAM.

The inequality  $0 \le \delta_w^{zk} + \alpha_w^{zk} \le 8$  and our choice to excavate up to 4 stack items per row of the execution trace allow our stack to deal with every instruction in one or two rows. The instruction decoded binary column <sup>⋄</sup>TWO\_LINE\_INSTRUCTION records precisely this hardcoded distinction. Most of the time instructions w with  $\delta_w^{zk} + \alpha_w^{zk} \leq 4$  have  ${}^{\lozenge}\mathsf{TLI} = 0$  though there are exceptions: CREATE and the three log instructions LOGO, LOG1 and LOG2 are counter-examples to this. We have chosen to deal with, on the one hand, CREATE and CREATE2, and on the other hand, the LOGX instructions,  $X \in \{0, \dots, 4\}$ , in unified ways.

<sup>&</sup>lt;sup>3</sup>and counter-constant by construction

<sup>&</sup>lt;sup>4</sup>More precisely:  $\delta_w \in \{0, 1, \dots, 7, 8, \dots, 17\}$  is the number of stack items w pops off of the current execution context's items w pushes onto the current execution context's stack given that doing so doesn't raise a stack overflow exception.

The value that was popped is pushed at both heights.

<sup>&</sup>lt;sup>6</sup>The popped values are interchanged in the pushes

$<sup>^7</sup>$ X - 1 for DUP\_X, X for SWAP\_X

If  ${}^{\Diamond}\mathsf{TLI} = 0$  and  $\delta^{\mathtt{zk}} + \alpha^{\mathtt{zk}} < 4$  fewer than 4 stack items are touched. Similarly, if  ${}^{\Diamond}\mathsf{TLI} = 1$  and  $\delta^{\mathtt{zk}} + \alpha^{\mathtt{zk}} < 8$ ) fewer than 8 stack items are touched. In either case we need to also impose constraints on the "phantom stack items". The consistency checks described in section 1.3.3 ignore such rows.

A slight complication arises from the CODECOPY instruction. This is an instruction with  $(\delta_w^{\mathbf{z}k}, \alpha_w^{\mathbf{z}k}) := (\delta_w, \alpha_w) = (3,0)$  and  ${}^{\Diamond}\mathsf{TLI} = 0$ . The stack pattern of this instruction is what one would expect from an instruction following the copyPattern. Except that its fourth stack item is only mostly empty. We exploit the absence of constraints that caracterizes stack items of any execution environment at HEIGHT = 0 (as well as any height of the  $0^{th}$  execution environment.) This allows us to introduce the current context's BC\_ADDR into the  ${}_{4}\mathsf{VAL}^{\mathsf{hi}}/{}_{4}\mathsf{VAL}^{\mathsf{lo}}$  fields without disturbance to stack consistency. The RETURN instruction, which is a  $(\delta_w^{\mathsf{z}k}, \alpha_w^{\mathsf{z}k}) := (\delta_w, \alpha_w) = (2,0)$  and  ${}^{\Diamond}\mathsf{TLI} = 0$  instruction, comes with a similar complication. If the current execution context isn't a deployment context (i.e. CTYPE = 0) then its fourth stack item is empty. If the current execution context is a deployment context (i.e. CTYPE = 1) its fourth stack item is  $mostly\ empty$ . As before we plug the current context's BC\_ADDR into the  ${}_{4}\mathsf{VAL}^{\mathsf{hi}}/{}_{4}\mathsf{VAL}^{\mathsf{lo}}$  fields and keep all other fields of the fourth stack item empty (i.e. = 0.) Again, this is without consequence for stack consistency constraints.

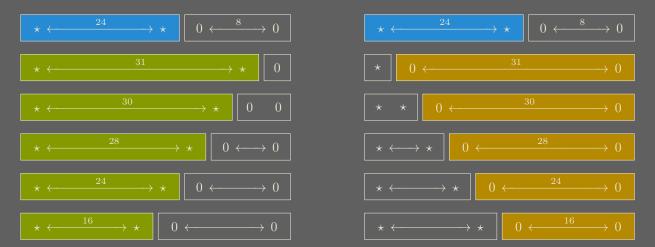

Here is an example: say the instruction pops  $\delta^{zk} = 2$  items and adds  $\alpha^{zk} = 1$  items and  ${}^{\diamondsuit}\mathsf{TLI} = 0$  (i.e. it's a "one line instruction".) This stack pattern applies to most arithmetic operations, most word comparison operations and most binary operations which have two inputs and one output. Note that  ${}^{\diamondsuit}\mathsf{TLI} = 0$  and  $\delta^{zk} + \alpha^{zk} = 3 < 4$  so there is one "phantom stack item" (the third one). The associated stack pattern will impose values to all 4 stack items that the present line "excavates" like in figure ??

| $\langle INST \rangle$ | $  \diamond_{TLI_i}  $ | HEIGHT               | $HEIGHT^{ u}$      | STACK□                          | $oxed{STACK}^ u$    | <sub>1</sub> ITEM              | <sub>2</sub> ITEM   | <sub>3</sub> ITEM | <sub>4</sub> ITEM    |

|------------------------|------------------------|----------------------|--------------------|---------------------------------|---------------------|--------------------------------|---------------------|-------------------|----------------------|

| BLA                    | 0                      | h                    | h — 1              | st                              | st + <b>3</b>       | • • • •                        |                     | Ø                 |                      |

|                        |                        | <sub>1</sub> ITEM    |                    |                                 |                     |                                | <sub>2</sub> ITEM   |                   |                      |

| 1HEIGH                 | $IT \mid_{1} VA$       | L <sup>hi</sup> 1VAL | ° <sub>1</sub> POP | □STACK                          | <sub>2</sub> HEIGHT | <sub>2</sub> VAL <sup>hi</sup> | $_2$ VAL $^{lo}$    | <sub>2</sub> POP  | $^\square_2$ STACK   |

| h — 0                  | $v_1^{\dagger}$        | $v_1^{lo}$           | 1                  | st + 1                          | h-1                 | $v_2^{hi}$                     | $v_2^{lo}$          | 1                 | st + 2               |

|                        |                        | <sub>3</sub> ITEM    |                    |                                 |                     |                                | <sub>4</sub> ITEM   |                   |                      |

| <sub>3</sub> HEIGH     | IT ∣₃VA                | L <sup>hi</sup> 3VAL | ° <sub>3</sub> POP | <sup>□</sup> <sub>3</sub> STACK | 4HEIGHT             | <sub>4</sub> VAL <sup>hi</sup> | <sub>4</sub> VAL lo | <sub>4</sub> POP  | □ <sub>4</sub> STACK |

| Ø                      | Ø                      | Ø                    | Ø                  | Ø                               | h-1                 | $v_4^{hi}$                     | $v_4^{lo}$          | 0                 | st + 3               |

Figure 1.1: The values in this font represent hardcoded values associated with this particular stack pattern. The values in this font are also hardcoded values but we reserve this font for empty stack items. Note that we consistently write  $\emptyset$  to mean 0 when a field of a particular stack item is zero because the stack item is empty, see section 1.3.3.

#### 1.3.2 Expected outcome

Designing stack patterns is straightforward for instructions pertaining to the binary module, the word comparison module, the arithmetic module and the storage module: the relevant instructions are relatively uniform in the number of arguments they retrieve from stack. There is more diversity for instructions touching the RAM and the call stack. Of the instructions directly touching RAM (or transaction call data) we want to achieve the following data pattern for instructions with  ${}^{\Diamond}TLI = 0$ : While for instructions touching RAM that require two lines (i.e.  ${}^{\Diamond}TLI = 1$ ): We also list the expected stack patterns for instructions that induce changes in the call stack:

| INST           | Item 1      | Item 2           | Item 3 | Item 4    |

|----------------|-------------|------------------|--------|-----------|

| CALLDATALOAD   | offset      | Ø                | Ø      | loaded    |

| MLOAD          | offset      | Ø                | Ø      | loaded    |

| MSTORE         | offset      | Ø                | Ø      | toStore   |

| MSTORE8        | offset      | Ø                | Ø      | toStore   |

| SLOAD          | storage key | Ø                | Ø      | loaded    |

| SSTORE         | storage key | Ø                | Ø      | toStore   |

| CALLDATACOPY   | offset      | (rel.) srcOffset | size   | Ø         |

| CODECOPY       | offset      | srcOffset        | size   | (address) |

| EXTCODECOPY    | offset      | srcOffset        | size   | address   |

| RETURNDATACOPY | offset      | (rel.) srcOffset | size   | Ø         |

| SHA3           | offset      | Ø                | size   | hash      |

| RETURN         | offset      | Ø                | size   | (address) |

| REVERT         | offset      | Ø                | size   | Ø         |

Figure 1.2: Expected stack patterns for 1 line instructions touching the RAM module. We have already alluded to the special case of CODECOPY and its mostly empty fourth stack item. The property of being mostly empty (i.e. only containing address := BYTECODE\_ADDRESS) is signaled by parentheses. We also signaled the same mostly empty fourth stack item issue with RETURN instructions ran in a deployment context. The interpretation of address := BYTECODE\_ADDRESS is analoguous in this case, but now depends on the binary flag CTYPE.

| INST    | Item 1 | Item 2 | Item 3 | Item 4         | СТ |

|---------|--------|--------|--------|----------------|----|

| LOGO    | offset | Ø      | size   | Ø              | 0  |

|         |        |        | Ø      | Ø              | 1  |

| LOG1    | offset | Ø      | size   | Ø              | 0  |

|         | topic1 |        | Ø      | Ø              | 1  |

| LOG2    | offset | Ø      | size   | Ø              | 0  |

|         | topic1 | topic2 | Ø      | Ø              | 1  |

| LOG3    | offset | Ø      | size   | Ø              | 0  |

|         | topic1 | topic2 | topic3 | Ø              | 1  |

| LOG4    | offset | Ø      | size   | Ø              | 0  |

|         | topic1 | topic2 | topic3 | topic4         | 1  |

| CREATE  | offset | Ø      | size   | address (or 0) | 0  |

|         | Ø      |        | value  | Ø              | 1  |

| CREATE2 | offset | salt   | size   | address (or 0) | 0  |

|         | Ø      | Ø      | value  | Ø              | 1  |

Figure 1.3: Expected stack pattern for instructions with  $^{\Diamond}$ TWO\_LINE\_INSTRUCTION = 1 touching the RAM module

| INST         | Item 1 | Item 2  | Item 3 | Item 4  | СТ |

|--------------|--------|---------|--------|---------|----|

| CALL         | offset | R@O     | size   | R@C     | 0  |

|              | gas    | address | value  | success |    |

| CALLCODE     | offset | R@O     | size   | R@C     | 0  |

|              | gas    | address | value  | success | 1  |

| DELEGATECALL | offset | R@O     | size   | R@C     | 0  |

|              | gas    | address | Ø      | success | 1  |

| STATICCALL   | offset | R@O     | size   | R@C     | 0  |

|              | gas    | address | Ø      | success | 1  |

Figure 1.4: Expected stack pattern for instructions with  $^{\Diamond}\mathsf{TWO\_LINE\_INSTRUCTION} = 1$  that don't touch the RAM module.

#### 1.3.3 Empty stack item

Let  $k \in \{1, 2, 3, 4\}$ . We define the following "empty k-th stack item" constraint system:

$${}_{k} \texttt{EmptyStackItem} \iff \left\{ \begin{array}{l} {}_{k} \texttt{HEIGHT}_{i} = 0 \\ {}_{k} \texttt{POP}_{i} = 0 \\ {}_{k} \texttt{VAL}^{\mathsf{hi}}{}_{i} = 0 \\ {}_{k} \texttt{VAL}^{\mathsf{lo}}{}_{i} = 0 \\ {}_{k} \texttt{STACK}_{i} = 0 \end{array} \right.$$

#### 1.3.4 Stack exception pattern

We lay out the constraints and stack pattern associated to stack exceptions.

```

1. IF STX_i = 1 THEN

```

Stack Item  $n^{\circ}1$ : The first stack item is empty: \_1EmptyStackItem

**Stack Item**  $n^{\circ}$  2: The second item is empty: <sub>2</sub>EmptyStackItem;

**Stack Item**  $n^{\circ}$  3: The third item is empty: <sub>3</sub>EmptyStackItem;

Stack Item n° 4: The fourth stack item is empty: 4EmptyStackItem;

Stack stamp update: STACK $\square^{\nu}_{i} = STACK\square_{i}$ ;

Height update:  $HEIGHT_i^{\nu} = 0$ ;

## 1.4 One line instruction stack patterns

#### 1.4.1 Disclaimer

The stack patterns presented in the current section 1.4 apply if and only if  $STX_i = 0$ .

#### $1.4.2 \quad (0,0)$ -pattern

**Supported instructions.** The 0\_0\_Pattern corresponds to evm instructions w with  $(\delta_w^{\mathbf{zk}}, \alpha_w^{\mathbf{zk}}) := (\delta_w, \alpha_w) = (0, 0)$ , i.e.

1. STOP;

3. JUMPDEST;

2. INVALID;

4. any byte that isn't an opcode.

**Relevant instruction decoded columns.** Among all instruction decoded columns we focus on the following flags:

| INST               | <sup>♦</sup> PAT | ♦TLI |

|--------------------|------------------|------|

| (0,0)-instructions | 0_0_Pattern      | 0    |

Constraints. We collect under the O\_O\_Pattern moniker the following collection of constraints:

Stack Item  $n^{\circ}1$ : The first stack item is empty: <sub>1</sub>EmptyStackItem;

Stack Item  $n^{\circ}$  2: The second stack item is empty: <sub>2</sub>EmptyStackItem;

Stack Item  $n^{\circ}$  3: The third stack item is empty: <sub>3</sub>EmptyStackItem;

Stack Item  $n^{\circ}$  4: The fourth stack item is empty:  ${}_{4}$ EmptyStackItem;  ${}_{2}$ EmptyStackItem,  ${}_{3}$ EmptyStackItem and  ${}_{4}$ EmptyStackItem,

Stack stamp update:  $STACK\square^{\nu}_{i} = STACK\square_{i}$ ,

Height update:  $HEIGHT^{\nu}_{i} = HEIGHT_{i}$ ,

### $1.4.3 \quad (0,1) \text{ and } (1,0) \text{ patterns}$

**Supported instructions.** The instructions listed below are precisely the instructions with  $^{\Diamond}\mathsf{PAT} = \mathsf{oneItemPattern}$ . The oneItemPattern corresponds to even instructions w with  $(\delta_w, \alpha_w) \in \{(1,0), (0,1)\}$ , i.e. (1,0)-instructions. For such instructions  $(\delta_w^{\mathtt{zk}}, \alpha_w^{\mathtt{zk}}) := (\delta_w, \alpha_w)$  and  $^{\Diamond}\mathsf{TLI} = 0$ . The (1,0)-instructions are:

1. POP

2. JUMP

3. SELFDESTRUCT

and (0,1)-instructions:

1. ADDRESS

8. RETURNDATASIZE

15. SELFBALANCE

2. ORIGIN

9. COINBASE

16. BASEFEE

3. CALLER

$10.\ {\tt TIMESTAMP}$

17. PC

4. CALLVALUE

11. NUMBER

18. MSIZE

$5. \ {\tt CALLDATASIZE}$

12. DIFFICULTY

19. GAS

6. CODESIZE

13. GASLIMIT

20. PUSH1-PUSH32

7. GASPRICE

14. CHAINID

**Relevant instruction decoded columns.** Among all instruction decoded columns we focus on the following flags:

| INST               | ♦PAT           | ♦TLI | $^{\diamond}$ FLAG $^{1}$ |

|--------------------|----------------|------|---------------------------|

| (0,1)-instructions | oneItemPattern | 0    | 0                         |

| (1,0)-instructions | oneItemPattern | 0    | 1                         |

Graphical representation. We figures below represent the oneItemPattern stack pattern:

|                                                                 | Stack  | Stack  | Stack  | Stack  |

|-----------------------------------------------------------------|--------|--------|--------|--------|

|                                                                 | Item 1 | Item 2 | Item 3 | Item 4 |

| $_k$ HEIGHT $_i$                                                | Ø      | Ø      | Ø      | h+1    |

| <sub>k</sub> VAL <sup>hi</sup> / <sub>k</sub> VAL <sup>lo</sup> | Ø      | Ø      | Ø      | res    |

| $_k$ POP $_i$                                                   | Ø      | Ø      | Ø      | 0      |

| $\square_k$ STACK $_i$                                          | Ø      | Ø      | Ø      | st+1   |

|                         | Stack  | Stack  | Stack  | Stack  |

|-------------------------|--------|--------|--------|--------|

|                         | Item 1 | Item 2 | Item 3 | Item 4 |

| kHEIGHT $i$             | h      | Ø      | Ø      | Ø      |

| $k VAL^{hi}/k VAL^{lo}$ | top    | Ø      | Ø      | Ø      |

| $kPOP_i$                | 1      | Ø      | Ø      | Ø      |

| $\bigcap_k$ STACK $_i$  | st+1   | Ø      | Ø      | Ø      |

Figure 1.5: The left hand side represents the stack pattern for (0,1)-instructions (i.e.  ${}^{\Diamond}\mathsf{FLAG}^1=0$ ), the right hand side represents the stack pattern for (1,0)-instructions (i.e.  ${}^{\Diamond}\mathsf{FLAG}^1=1$ ) We write  $\mathsf{h}=\mathsf{HEIGHT}_i$  and  $\mathsf{STACK}\square_i=\mathsf{st}$ .

**Constraints.** We collect under the oneItemPattern moniker the following collection of constraints. They apply whenever

$$\mathsf{STX}_i = 0$$

**Stack Item**  $n^{\circ}1$ : The first stack item is contains a stack item *iff*  ${}^{\diamond}\mathsf{FLAG}^1=1$ :

$$\begin{cases} \ _{1}\mathsf{HEIGHT}_{i} &=& \mathsf{HEIGHT}_{i} \cdot {}^{\lozenge}\mathsf{FLAG}^{1}, \\ \ _{1}\mathsf{POP}_{i} &=& {}^{\lozenge}\mathsf{FLAG}^{1}, \\ \ _{1}^{\square}\mathsf{STACK}_{i} &=& (\mathsf{STACK}\square_{i}+1) \cdot {}^{\lozenge}\mathsf{FLAG}^{1}. \end{cases}$$

Stack Item  $n^{\circ}$  2: The second item is empty: <sub>2</sub>EmptyStackItem;

Stack Item  $n^{\circ}$  3: The third item is empty: <sub>3</sub>EmptyStackItem;

**Stack Item**  $n^{\circ}$  4: The fourth stack item is contains a stack item iff  ${}^{\diamond}\mathsf{FLAG}^1 = 0$ :

$$\begin{cases} \ _{4}\mathsf{HEIGHT}_{i} &=& (\mathsf{HEIGHT}_{i}+1)\cdot(1-{}^{\Diamond}\mathsf{FLAG}^{1}), \\ \ _{4}^{4}\mathsf{POP}_{i} &=& 0, \\ \ _{4}^{\square}\mathsf{STACK}_{i} &=& (\mathsf{STACK}\square_{i}+1)\cdot(1-{}^{\Diamond}\mathsf{FLAG}^{1}). \end{cases}$$

Stack stamp update:  $STACK\square^{\nu}_{i} = STACK\square_{i} + 1$ ;

Height update:  $\mathsf{HEIGHT}^{\nu}_{i} = \mathsf{HEIGHT}_{i} + (1 - 2 \cdot {}^{\Diamond}\mathsf{FLAG}^{1});$

### 1.4.4 (1,1) and (2,0) patterns

**Supported instructions.** The stack pattern described below applies to the following instructions (1,1)-instructions:

• ISZERO

• BLOCKHASH

• NOT

• CALLDATALOAD

• BALANCE

MLOAD

• EXTCODESIZE

• SLOAD

• EXTCODEHASH

and to the following (2,0)-instructions:

• MSTORE • SSTORE

• MSTORE8 • JUMPI

**Relevant instruction decoded columns.** Among all instruction decoded columns we focus on the following:

| INST               | ♦PAT           | ♦TLI | $^{\diamond}$ FLAG $^{1}$ |

|--------------------|----------------|------|---------------------------|

| (1,1) instructions | twoItemPattern | 0    | 0                         |

| (2,0) instructions | twoItemPattern | 0    | 1                         |

**Graphical representation.** The picture is the following, for instance for MLOAD ( ${}^{\Diamond}$ FLAG<sup>1</sup> = 0) and MSTORE ( ${}^{\Diamond}$ FLAG<sup>1</sup> = 1)

|                                                                 | Stack  | Stack  | Stack  | Stack  |

|-----------------------------------------------------------------|--------|--------|--------|--------|

|                                                                 | Item 1 | Item 2 | Item 3 | Item 4 |

| $_k$ HEIGHT $_i$                                                | h      | Ø      | Ø      | h      |

| <sub>k</sub> VAL <sup>hi</sup> / <sub>k</sub> VAL <sup>lo</sup> | ARG1   | Ø      | Ø      | OUT    |

| $_k$ POP $_i$                                                   | 1      | Ø      | Ø      | 0      |

| $\square_k$ STACK $_i$                                          | st+1   | Ø      | Ø      | st + 2 |

|                                                              | Stack  | Stack  | Stack  | Stack  |

|--------------------------------------------------------------|--------|--------|--------|--------|

|                                                              | Item 1 | Item 2 | Item 3 | Item 4 |

| kHEIGHT $i$                                                  | h      | Ø      | Ø      | h-1    |

| <sub>k</sub> VAL hi/ <sub>k</sub> VAL lo                     | ARG1   | Ø      | Ø      | ARG2   |

| $_k$ POP $_i$                                                | 1      | Ø      | Ø      | 1      |

| $\begin{bmatrix} \Box \\ k \end{bmatrix}$ STACK <sub>i</sub> | st+1   | Ø      | Ø      | st + 2 |

Figure 1.6: On the left hand side is the picture for a (1,1) instruction (i.e.  ${}^{\Diamond}\mathsf{FLAG}^1=0$ ). On the right hand side is the picture for a (2,0) instruction (i.e.  ${}^{\Diamond}\mathsf{FLAG}^1=1$ ). We write  $\mathsf{h}=\mathsf{HEIGHT}_i$  and  $\mathsf{STACK}\square_i=\mathsf{st}$ .

Constraints. We collect under the two ItemPattern moniker the following collection of constraints:

Stack Item  $n^{\circ}$ 1: depending on the instruction contains either a relative offset, an absolute offset or a storage key:

$$\begin{cases} \ _1\mathsf{HEIGHT}_i &= \ \mathsf{HEIGHT}_i, \\ \ _1\mathsf{POP}_i &= \ 1, \\ \ _1\mathsf{STACK}_i &= \ \mathsf{STACK}\square_i + 1. \end{cases}$$

**Stack Item**  $n^{\circ}$  2: is empty: <sub>2</sub>EmptyStackItem;

Stack Item  $n^{\circ} 3$ : is empty: <sub>3</sub>EmptyStackItem;

Stack Item  $n^{\circ}$  4: depending on the instruction, contains the value being loaded or being stored:

$$\left\{ \begin{array}{lll} {}_{4}\mathsf{HEIGHT}_{i} & = & \mathsf{HEIGHT}_{i} - {}^{\Diamond}\mathsf{FLAG}^{1} \\ {}_{4}\mathsf{POP}_{i} & = & {}^{\Diamond}\mathsf{FLAG}^{1} \\ {}_{4}^{\square}\mathsf{STACK}_{i} & = & \mathsf{STACK}\square_{i} + 2. \end{array} \right.$$

Stack stamp update: STACK $\square^{\nu}_{i} = STACK\square_{i} + 2$ ,

$\textbf{Height update: HEIGHT}_{i} = \textbf{HEIGHT}_{i} - 2 \cdot {}^{\diamondsuit} \textbf{FLAG}^{1},$

For this set of instructions the interpretation of  ${}^{\Diamond}\mathsf{FLAG}^1$  is that it equals 1 for storing instructions and 0 for loading instructions.

#### 1.4.5 (2,1) and (3,1) patterns

**Supported instructions.** The stack pattern described below applies to the following  $(\delta_w^{\mathbf{z}\mathbf{k}}, \alpha_w^{\mathbf{z}\mathbf{k}}) = (\delta_w, \alpha_w) = (2, 1)$  instructions:

| • ADD  | • MOD        | • GT  | • OR   | • SAR  |

|--------|--------------|-------|--------|--------|

| • MUL  | • SMOD       | • SLT | • XOR  | • SHA3 |

| • SUB  | • EXP        | • SGT | • BYTE |        |

| • DIV  | • SIGNEXTEND | • EQ  | • SHL  |        |

| • SDIV | • LT         | • AND | • SHR  |        |

as well as to the following  $(\delta_w^{\tt zk}, \alpha_w^{\tt zk}) = (\delta_w, \alpha_w) = (3,1)$  instructions:

• ADDMOD • MULMOD

Note that we *don't* include CREATE (which would have the correct signature ... maybe we should?) The purpose of the  ${}^{\Diamond}\mathsf{FLAG}^1$  is to differentiate between those instructions with 2 inputs ( ${}^{\Diamond}\mathsf{FLAG}^1=0$ ) and those instructions with 3 inputs ( ${}^{\Diamond}\mathsf{FLAG}^1=1$ .)

**Graphical representation.** The picture is the following:

|                                  | Stack  | Stack  | Stack  | Stack  |

|----------------------------------|--------|--------|--------|--------|

|                                  | Item 1 | Item 2 | Item 3 | Item 4 |

| $_k$ HEIGHT $_i$                 | h      | Ø      | h-1    | h-1    |

| $_{k}VAL^{hi}/_{k}VAL^{lo}$      | ARG1   | Ø      | ARG2   | OUT    |

| $_k$ POP $_i$                    | 1      | Ø      | 1      | 0      |

| $\bigcap_{k}$ STACK <sub>i</sub> | st+1   | Ø      | st + 2 | st + 3 |

|                                         | Stack  | Stack  | Stack  | Stack  |

|-----------------------------------------|--------|--------|--------|--------|

|                                         | Item 1 | Item 2 | Item 3 | Item 4 |

| kHEIGHT $i$                             | h      | h-2    | h-1    | h-2    |

| $k = \frac{1}{k} VAL^{hi} / k VAL^{lo}$ | ARG1   | ARG3   | ARG2   | OUT    |

| $_k$ POP $_i$                           | 1      | 1      | 1      | 0      |

| $\square_k$ STACK <sub>i</sub>          | st+1   | st + 2 | st + 3 | st+4   |

Figure 1.7: Representation of the standardPattern for  ${}^{\Diamond}\mathsf{FLAG}^1 = 0$  (left) and  ${}^{\Diamond}\mathsf{FLAG}^1 = 1$  (right.) On the left hand side standard instructions with 2 arguments, on the right hand side standard instructions with 3 arguments. We chose to put the second instruction argument in the third stack item because of the SHA3 instruction that, following expectations, expects to find its size parameter in the 3rd stack item. We write  $\mathsf{h} = \mathsf{HEIGHT}_i$  and  $\mathsf{STACK\Box}_i = \mathsf{st}$ .

Constraints. We collect under the 2\_1\_Pattern moniker the following collection of constraints:

**Stack Item**  $n^{\circ}$  1: contains the first instruction argument:

$$\begin{cases} \ _1\mathsf{HEIGHT}_i &= \ \mathsf{HEIGHT}_i, \\ \ _1\mathsf{POP}_i &= \ 1, \\ \ _1^\square\mathsf{STACK}_i &= \ \mathsf{STACK}_i + 1. \end{cases}$$

Stack Item  $n^{\circ}$  2: contains the second instruction argument:

$$\left\{ \begin{array}{lll} {}_{2}\mathsf{HEIGHT}_{i} & = & (\mathsf{HEIGHT}_{i}-2) \cdot {}^{\lozenge}\mathsf{FLAG}^{1}{}_{i}, \\ {}_{2}\mathsf{POP}_{i} & = & {}^{\lozenge}\mathsf{FLAG}^{1}{}_{i}, \\ {}_{2}^{\square}\mathsf{STACK}_{i} & = & (\mathsf{STACK}\square_{i}+2) \cdot {}^{\lozenge}\mathsf{FLAG}^{1}{}_{i} \end{array} \right.$$

Stack Item  $n^{\circ} 3$ :

$$\begin{cases} \ _{3}\mathsf{HEIGHT}_{i} &=& \mathsf{HEIGHT}_{i}-1, \\ \ _{3}\mathsf{POP}_{i} &=& 1, \\ \ _{3}^{\square}\mathsf{STACK}_{i} &=& \mathsf{STACK}_{\square}_{i}+2+{}^{\lozenge}\mathsf{FLAG}^{1}_{i}. \end{cases}$$

Stack Item  $n^{\circ}$  4: contains the output of the instruction

$$\begin{cases} \ _{4}\mathsf{HEIGHT}_{i} &=& \mathsf{HEIGHT}_{i} - 1 - {}^{\diamondsuit}\mathsf{FLAG}^{1}{}_{i}, \\ \ _{4}\mathsf{POP}_{i} &=& 0, \\ \ _{4}^{\square}\mathsf{STACK}_{i} &=& \mathsf{STACK}_{\square}{}_{i} + 3 + {}^{\diamondsuit}\mathsf{FLAG}^{1}. \end{cases}$$

Stack stamp update:  $STACK\square^{\nu}_{i} = STACK\square_{i} + 3 + {}^{\Diamond}FLAG^{2}_{i};$

Height update:  $\mathsf{HEIGHT}^{\nu}_{i} = \mathsf{HEIGHT}_{i} - 1 - \mathsf{FLAG}^{1}_{i};$

#### 1.4.6 DUP\_X-pattern

Supported instructions. The dupPattern is used by DUP\_X,  $X \in \{1, 2, ..., 16\}$ , instructions.

**Relevant instruction decoded columns.** Among all instruction decoded columns we only require the  $^{\Diamond}$ INST\_PARAMETER column:

| INST  | ♦PAT       | ♦TLI | <sup>♦</sup> PARAM |

|-------|------------|------|--------------------|

| DUP_X | dupPattern | 0    | X-1                |

Graphical representation. The figure below represents the dupPattern stack pattern:

|                                 | Stack                  | Stack  | Stack                  | Stack  |

|---------------------------------|------------------------|--------|------------------------|--------|

|                                 | Item 1                 | Item 2 | Item 3                 | Item 4 |

| $_k$ HEIGHT $_i$                | h – <sup>♦</sup> PARAM | Ø      | h − <sup>♦</sup> PARAM | h+1    |

| $_k$ VAL $^{hi}/_k$ VAL $^{lo}$ | v                      | Ø      | v                      | v      |

| $_k$ POP $_i$                   | 1                      | Ø      | 0                      | 0      |

| $\bigcap_k$ STACK <sub>i</sub>  | st+1                   | Ø      | st+2                   | st + 3 |

Figure 1.8: The stack pattern for DUP\_X instructions. We write  $h = HEIGHT_i$  and  $st = STACK\Box_i$ .

Constraints. We collect under the dupPattern moniker the following collection of constraints:

1. First stack item:

$$\left\{ \begin{array}{l} {}_{1}\mathsf{HEIGHT}_{i} = \mathsf{HEIGHT}_{i} - {}^{\Diamond}\mathsf{PARAM}_{i}, \\ {}_{1}\mathsf{POP}_{i} = 1, \\ {}_{1}^{\square}\mathsf{STACK}_{i} = \mathsf{STACK}_{1} + 1. \end{array} \right.$$

- 2. Second stack item: <sub>2</sub>EmptyStackItem.

- 3. Third stack item:

$$\left\{ \begin{array}{l} {}_{3}\mathsf{HEIGHT}_{i} = \mathsf{HEIGHT}_{i} - {}^{\lozenge}\mathsf{PARAM}_{i}, \\ {}_{3}\mathsf{POP}_{i} = 0, \\ {}_{3}\mathsf{VAL}^{\mathsf{hi}}{}_{i} = {}_{1}\mathsf{VAL}^{\mathsf{hi}}{}_{i} \\ {}_{3}\mathsf{VAL}^{\mathsf{lo}}{}_{i} = {}_{1}\mathsf{VAL}^{\mathsf{lo}}{}_{i} \\ {}_{3}\mathsf{STACK}_{i} = \mathsf{STACK}\square_{i} + 2. \end{array} \right.$$

4. Fourth stack item:

$$\begin{cases} \ _{4}\mathsf{HEIGHT}_{i} = \mathsf{HEIGHT}_{i} + 1, \\ \ _{4}\mathsf{POP}_{i} = 0, \\ \ _{4}\mathsf{VAL}^{\mathsf{hi}}{}_{i} = {}_{1}\mathsf{VAL}^{\mathsf{hi}}{}_{i} \\ \ _{4}\mathsf{VAL}^{\mathsf{lo}}{}_{i} = {}_{1}\mathsf{VAL}^{\mathsf{lo}}{}_{i} \\ \ _{4}\mathsf{STACK}_{i} = \mathsf{STACK}\square_{i} + 3. \end{cases}$$

- 5.  $\mathsf{STACK}\square^{\nu}{}_{i} = \mathsf{STACK}\square_{i} + 3,$

- 6.  $\mathsf{HEIGHT}^{\nu}_{i} = \mathsf{HEIGHT}_{i} + 1$ ,

#### 1.4.7 SWAP\_X-pattern

Supported instructions. The swapPattern is used by SWAP\_X,  $X \in \{1, 2, ..., 16\}$ , instructions.

**Relevant instruction decoded columns.** Among all instruction decoded columns we only require the  $^{\Diamond}$ INST\_PARAMETER column:

| INST   | <sup>♦</sup> PAT | ♦TLI | ◇PARAM |

|--------|------------------|------|--------|

| SWAP_X | swapPattern      | 0    | Х      |

Graphical representation. The figure below represents the swapPattern stack pattern:

|                                     | Stack                  | Stack  | Stack                  | Stack  |

|-------------------------------------|------------------------|--------|------------------------|--------|

|                                     | Item 1                 | Item 2 | Item 3                 | Item 4 |

| $_k$ HEIGHT $_i$                    | h – <sup>♦</sup> PARAM | h      | h – <sup>♦</sup> PARAM | h      |

| $_{k}$ VAL $^{hi}/_{k}$ VAL $^{lo}$ | v                      | v'     | v'                     | v      |

| $_k$ POP $_i$                       | 1                      | 1      | 0                      | 0      |

| $\square_k$ STACK $_i$              | st+1                   | st + 2 | st + 3                 | st+4   |

Figure 1.9: The stack pattern for DUP\_X instructions. We write  $h = \mathsf{HEIGHT}_i$  and  $\mathsf{st} = \mathsf{STACK}\square_i$ .

Constraints. We collect under the swapPattern moniker the following collection of constraints:

1. First stack item:

$$\left\{ \begin{array}{l} {}_{1}\mathsf{HEIGHT}_{i} = \mathsf{HEIGHT}_{i} - {}^{\lozenge}\mathsf{PARAM}_{i}, \\ {}_{1}\mathsf{POP}_{i} = 1, \\ {}_{1}^{\square}\mathsf{STACK}_{i} = \mathsf{STACK}\square_{i} + 1. \end{array} \right.$$

2. Second stack item:

$$\begin{cases} \ _2\mathsf{HEIGHT}_i = \mathsf{HEIGHT}_i, \\ \ _2\mathsf{POP}_i = 1, \\ \ _2^\mathsf{STACK}_i = \mathsf{STACK}\square_i + 2. \end{cases}$$

3. Third stack item:

$$\begin{cases} \ _{3}\mathsf{HEIGHT}_{i} = \mathsf{HEIGHT}_{i} - ^{\lozenge}\mathsf{PARAM}_{i}, \\ _{3}\mathsf{POP}_{i} = 0, \\ _{3}\mathsf{VAL}^{\mathsf{hi}}{}_{i} = _{2}\mathsf{VAL}^{\mathsf{hi}}{}_{i} \\ _{3}\mathsf{VAL}^{\mathsf{lo}}{}_{i} = _{2}\mathsf{VAL}^{\mathsf{lo}}{}_{i} \\ _{3}\mathsf{STACK}_{i} = \mathsf{STACK}\square_{i} + 3. \end{cases}$$

4. Fourth stack item: